GPS/GNSS Chips

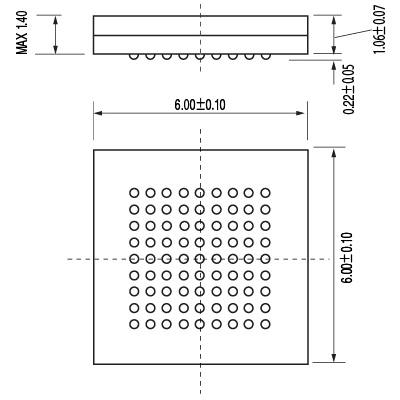

GPS Receiver Chip eRideOPUS 5 Model ePV5900B Discontinued Products

Ultra high-sensitivity, single-die GPS/A-GPS receiver chip

eRideOPUS 5 (ePV5900B) is a high-sensitivity

GPS/AGPS receiver System-in-a-Package (SiP) that combines single-die receiver with integrated flash memory. It delivers fast, accurate positioning data in challenging locations such as indoor environments and deep urban canyons.

Automotive/Industrial